### **Features**

- 3.4V to 5.5V input range for Efficient Linear Charging

- Programmable Charging Current from 10mA to 500mA by 0.1% external resistor

- Low Dropout Fast Charge, up to 1.5A

- Configurable 4V 4.525V charging voltage. Preset 4.2V with ±0.5% Accuracy

- Fully Integrated Power Path Switches and No External Blocking Diode Required

- Charging/Discharging Current Monitor Output for Fuel Gauging

- Device Status Output and Access Command Input from STACMD pin

- C/20 Charge Termination

- 2.8V Trickle Charge Threshold

- Built-In Battery Disconnection Function for Shipping Mode with 150nA current consumption

- Built-In Robust Protection Including Input Current Limit, System Short-Circuit Protection, Discharge Current Limit, Battery OVP, Thermal Regulation

- Safety Related Certifications: IEC62368-1:2018 CB Certification

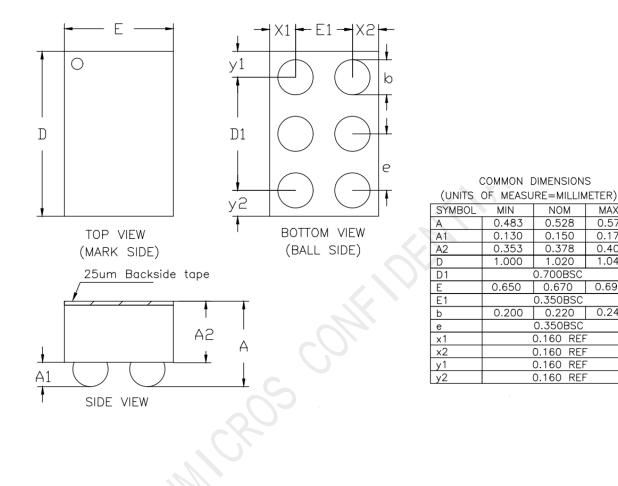

- Tiny 0.67mm x 1.02mm 6-pin WLP with 0.35mm pitch

### Applications

- Smart Watch/Band

- TWS Earbud

- Bluetooth Portable Device

### **General Description**

YHM2710 is a highly integrated, single-cell Li-ion battery charger with system power path management for space-limited portable applications. The full charger function features Trickle-charge, constant current fast charge and constant voltage regulation, charge termination, and auto recharge.

YHM2710 can deliver up to 500mA charging current, be programmed externally with a single resistor. The charge voltage is default 4.2V and adjustable by Access command. YHM2710 automatically terminates the charge cycle when the charge current drops to 1/20 of the programmed value after the final float voltage is reached. The device can report charging/discharging current for fuel gauging by current monitor output.

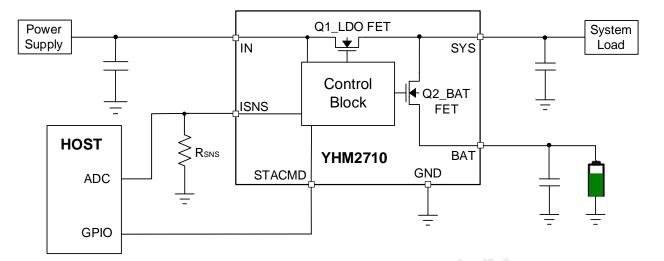

Fully Integrated Power Path Switches and no blocking diode is required due to the internal bi-direction MOSFET architecture. Thermal feedback regulates the charge current to limit the die temperature during high power operation or high ambient temperature.

YHM2710 can enter shipping mode by Access command and exit it after input power is present. In shipping mode, battery FET is open and the device only consume 150nA current.

The device status is indicated on STACMD pin output for charging, discharging and charge done. This pin also supports Access command to adjust charging current and charging voltage or enter different mode.

YHM2710 comes in a 6-bump, 0.35mm pitch, 0.67mm x1.02mm wafer-level package (WLP).

Fig 1. YHM2710 Typical Application

#

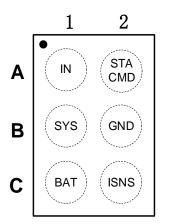

### YHM2710 Pin Configurations

### Fig 2. YHM2710 WLP-6 Pin Assignment(Top Through View)

# YHM2710 WLP Pin Descriptions

| WLP | Name   | Description                                                                                                                                                                                        |  |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1  | IN     | Input and Power Supply. Bypass this input with a ceramic capacitor to ground.                                                                                                                      |  |  |  |

| A2  | STACMD | Status Output and Access Command Input. This pin can also be used<br>push button for hardware reset or exit ship mode, connect push button<br>50kohm resistor.                                     |  |  |  |

| B1  | SYS    | System power supply. Connect to system load. Place at least $4.7\mu F$ ceramic capacitor from SYS to GND, and as close to the IC as possible.                                                      |  |  |  |

| B2  | GND    | Ground.                                                                                                                                                                                            |  |  |  |

| C1  | BAT    | Battery Pin. Place at least 2.2 $\mu$ F ceramic capacitor from BAT to GND, and as close to the IC as possible.                                                                                     |  |  |  |

| C2  | ISNS   | Charge Current Program & Monitor Pin. The charge current is programmed<br>by connecting a 0.1% resistor to GND. The voltage on this pin can be used<br>to measure the current between BAT and SYS. |  |  |  |

### Function Table

| STACMD PIN | Status                       |

|------------|------------------------------|

| Low        | Charging                     |

| High       | Other Status except Charging |

### 1 Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

Disclaimer: YHMICROS reserves the right to make any change in circuit design, specification or other related things if needed without notice at any time.

| Symbol           | Parame                                                                      | eters                                    | Min. | Max.                  | Unit |  |

|------------------|-----------------------------------------------------------------------------|------------------------------------------|------|-----------------------|------|--|

| Vin              | IN to GND                                                                   |                                          | -0.3 | 6                     | V    |  |

| Vsys             | SYS to GND                                                                  |                                          | -0.3 | V <sub>IN</sub> + 0.3 | V    |  |

| VOTHER           | Other Pin to GND                                                            |                                          | -0.3 | 6                     | V    |  |

| lın              | Input Current                                                               |                                          | 0    | 1500                  | mA   |  |

| T <sub>STG</sub> | Storage Junction Temperature                                                | Storage Junction Temperature             |      |                       |      |  |

| TJ               | Operating Junction Temperature                                              | Operating Junction Temperature           |      |                       |      |  |

| ΤL               | Lead Temperature (Soldering, 1                                              | Lead Temperature (Soldering, 10 Seconds) |      |                       |      |  |

| θ <sub>JA</sub>  | Thermal Resistance, Junction-to<br>(100mm <sup>2</sup> pad of 1 oz. copper) | p-Ambient                                |      | TBD                   | °C/W |  |

|                  | Electrostatic Discharge                                                     | Human Body Model,<br>EIA/JESD22-A114     | 2    |                       |      |  |

| All Pins         | Capability                                                                  | Charged Device Model,<br>JESD22-C101     | 1    |                       | - KV |  |

Note 1. Refer to JEDEC JESD51-7, use a 4-layerboard

### 2 Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance.

| Parameters                                                                    | Min. | Max.  | Unit |

|-------------------------------------------------------------------------------|------|-------|------|

| Vin                                                                           | 3.4  | 5.5   | V    |

| l <sub>IN</sub>                                                               | 0    | 550   | mA   |

| Ідіясна                                                                       | 0    | 1500* | mA   |

| Існа                                                                          | 10   | 500   | mA   |

| Vother                                                                        | 0    | 5.5   | V    |

| Cin                                                                           | 0.1  |       | μF   |

| $C_{\text{SYS}}$ (at least 3µF of ceramic capacitance with DC bias de-rating) | 4.7  |       | μF   |

| C <sub>BAT</sub>                                                              | 2.2  |       | μF   |

| Ambient Operating Temperature, T <sub>A</sub>                                 | -40  | 85    | °C   |

| Operating Junction Temperature, T <sub>J</sub>                                | -40  | 150   | °C   |

\*1.5A continuous discharge current in 85°C. Peak 2.5A 10ms.

### **3** Detailed Electrical Characteristics

$(V_{IN} = 5V, V_{BAT} = 3.7V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted) (Note 1)

| PARAMETER                                                  | SYMBOL                   | CONDITIONS                                                | MIN  | TYP   | MAX | UNITS |

|------------------------------------------------------------|--------------------------|-----------------------------------------------------------|------|-------|-----|-------|

| Input and Power Path                                       |                          |                                                           | •    |       |     | •     |

| Input Voltage Range                                        | Vin                      |                                                           | 3.4  |       | 5.5 | V     |

| Input Undervoltage Lockout<br>Threshold                    | Vin_uvlo                 | Input Falling                                             |      | 3.2   |     | V     |

| Input Undervoltage Lockout<br>Threshold Hysteresis         | V <sub>IN_UVLO_HYS</sub> | Input Rising                                              |      | 200   |     | mV    |

| Input vs. Battery Voltage Headroom<br>Threshold            | Vhdrm                    | Input Rising vs. Battery                                  |      | 150   |     | mV    |

| Input vs. Battery Voltage Headroom<br>Threshold Hysteresis | Vhdrm_hys                |                                                           |      | 30    |     | mV    |

| Quiescent Supply Current                                   | I <sub>INQ</sub>         | T <sub>A</sub> =+25°C, Charge Mode                        |      | 0.5   |     | mA    |

| Quescent Supply Surrent                                    | IINQ                     | -40°C $\leq$ T <sub>A</sub> $\leq$ +85°C, Charge Mode     |      |       | 2   | ША    |

| IN to SYS switch on resistance                             | Ron_Q1                   | V <sub>IN</sub> = 5V, I <sub>SYS</sub> = 100mA            |      | 140   | 250 | mΩ    |

| Regulated SVS Output Valtage                               | V                        | 1.03×V <sub>REG</sub> (V <sub>REG</sub> =4.2V)            |      | 4.326 |     | V     |

| Regulated SYS Output Voltage                               | V <sub>SYS</sub>         | Accuracy, T <sub>A</sub> = +25°C                          | -2   |       | 2   | %     |

| Input Current Protection                                   | IIN_OCP                  |                                                           | 520  | 550   | 590 | mA    |

| Battery Charger                                            | L                        |                                                           |      |       |     | 1     |

|                                                            |                          | V <sub>IN</sub> = 5V, Charge Done, I <sub>SYS</sub> = 0mA |      | 2     |     | μA    |

|                                                            | Івато                    | $V_{IN} = 0V$ , $V_{BAT} = 4.35V$ , $I_{SYS} = 0mA$       |      | 20    |     | μA    |

| Battery Quiescent Current                                  |                          | Sleep Mode                                                |      | 150   | 500 | nA    |

|                                                            |                          | Shipping Mode                                             |      | 150   | 500 | nA    |

| Battery FET on resistance                                  | R <sub>ON_Q2</sub>       | $V_{IN} = 0V, V_{BAT} = 3.7V, I_{SYS} = 100mA$            |      | 50    |     | mΩ    |

|                                                            |                          | Default, $T_A = +25^{\circ}C$                             |      | 4.2   |     | V     |

| Battery Charge Voltage Regulation                          | Vreg                     | Accuracy, $T_A = +25^{\circ}C$                            | -0.5 |       | 0.5 | %     |

|                                                            |                          | $R_{SNS} = 25k\Omega$                                     |      | 20    |     |       |

|                                                            |                          | R <sub>SNS</sub> = 10kΩ                                   |      | 50    |     |       |

|                                                            |                          | $R_{SNS} = 5k\Omega$                                      |      | 100   |     | mA    |

| Fast Charge Current                                        | I <sub>REG</sub>         | $R_{SNS} = 2k\Omega$                                      |      | 250   |     |       |

|                                                            |                          | R <sub>SNS</sub> = 1kΩ                                    |      | 500   |     |       |

|                                                            |                          | Accuracy, $T_A = +25^{\circ}C$ , $R_{SNS} = 2k\Omega$     | -5   |       | 5   | %     |

| Regulation Junction Temperature<br>Threshold               | $T_{J_REG}$              |                                                           |      | 120   |     | °C    |

| Trickle-Charge Current                                     | Itrickle                 | =0.05×I <sub>REG</sub> , R <sub>SNS</sub> = 2k $\Omega$   |      | 12.5  |     | mA    |

| Trickle-Charge Threshold Voltage                           | VBAT_TRICKLE             | VBAT Rising                                               | 2.7  | 2.8   | 2.9 | V     |

| Trickle-Charge Threshold<br>Hysteresis                     |                          |                                                           |      | 100   |     | mV    |

| Pre-Charge Current                                         | IPRE                     |                                                           |      | 4     |     | mA    |

NOV, 2023

| Pre-Charge Threshold Voltage                           | VBAT_PRE                 | VBAT Rising                                            | 2     | V                |

|--------------------------------------------------------|--------------------------|--------------------------------------------------------|-------|------------------|

| Pre-Charge Threshold Hysteresis                        | _                        |                                                        | 100   | mV               |

| Termination Current Threshold                          | ITERM                    | =0.05×I <sub>REG</sub> , R <sub>SNS</sub> = $2k\Omega$ | 12.5  | mA               |

| Termination Deglitch Time                              | tterm_dgl                |                                                        | 32    | ms               |

| Battery Auto-recharge Voltage<br>Threshold             | VRECH                    | V <sub>BAT</sub> Falling                               | 200   | mV               |

| Battery Auto-recharge Voltage<br>Deglitch Time         | trech_dgl                |                                                        | 120   | ms               |

| Over Discharge Current Regulation                      | Idis_reg                 | =10×I <sub>REG</sub> , R <sub>SNS</sub> = $2k\Omega$   | 2500  | mA               |

| Battery Undervoltage Lockout<br>Threshold              | Vbat_uvlo                | V <sub>BAT</sub> Falling                               | 2.4   | V                |

| Battery Undervoltage Lockout<br>Threshold Hysteresis   | VBAT_UVLO_HY<br>S        |                                                        | 200   | mV               |

| Battery Overvoltage Protection<br>Threshold            | V <sub>BAT_OVP</sub>     | V <sub>BAT</sub> Rising, higher than V <sub>REG</sub>  | 100   | mV               |

| Battery Overvoltage Protection<br>Threshold Hysteresis | V <sub>BAT_OVP_HYS</sub> |                                                        | 90    | mV               |

| System Voltage Threshold for Short Detection           | V <sub>SHORT</sub>       |                                                        | 2     | V                |

| Shipping Mode                                          |                          |                                                        |       |                  |

| Enter shipping mode deglitch time                      | tsmen_dgl                |                                                        | 1.5   | S                |

| THERMAL PROTECTION                                     |                          | $\mathcal{C}$                                          |       |                  |

| Thermal Shutdown                                       | T <sub>SHDN</sub>        |                                                        | 150   | ٥C               |

| Thermal Hysteresis                                     | T <sub>HYST</sub>        | 0                                                      | 20    | ٥C               |

| LOGIC                                                  | 0                        |                                                        |       |                  |

| High Voltage of ACMD                                   | VIH_ACMD                 | 1.8V Version                                           | 1.17  | V                |

| Low Voltage of ACMD                                    | VIL_ACMD                 |                                                        | 0.3   | V                |

| Output High Voltage of STACMD                          | VOH_STA                  |                                                        | 1.475 | V                |

| Output Low Voltage of STACMD                           | Vol_sta                  | Isink=5mA                                              | 0.15  | V                |

| ACMD Timing & Specification                            |                          |                                                        |       |                  |

| ACMD Line Pull up resistor                             | Rpull                    |                                                        | 10    | KΩ               |

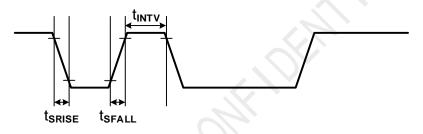

| Bit Period                                             | t <sub>віт</sub>         |                                                        | 300   | ns               |

| Logic 0                                                | t <sub>LOG0</sub>        |                                                        | 8     | t <sub>віт</sub> |

| Logic 1                                                | t∟og1                    |                                                        | 26    | tвıт             |

| Logic Z                                                | t∟ogz                    |                                                        | 60    | tвıт             |

| SWC Rising Time                                        | tsrise                   |                                                        | 0.5   | t <sub>віт</sub> |

| SWC Falling Time                                       | tsfall                   |                                                        | 0.5   | tвıт             |

| Two Bit interval                                       | tintv                    |                                                        | 1     | tвıт             |

|                                                        |                          |                                                        |       |                  |

**Note :** All specifications are 100% production tested at  $T_A = +25^{\circ}C$ , unless otherwise noted.

### 4 Detailed Description

#### 4.1 General Introduction

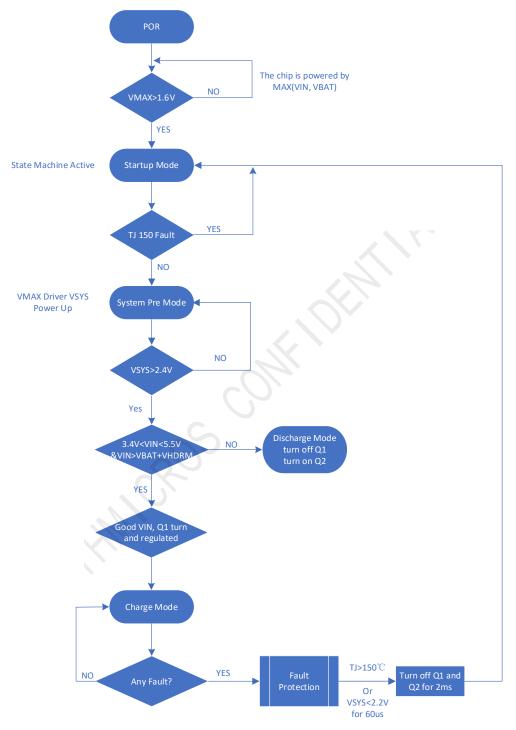

The YHM2710 is a highly integrated, single-cell Li-ion battery charger with system power path management. The full charger function features Trickle-charge, constant current fast charge and constant voltage regulation, charge termination, and auto recharge. The power path function allows the input source to power the system and charge the battery simultaneously. The device supports private Access command to configure charger without I<sup>2</sup>C. The internal bias circuit of the IC is powered from V<sub>MAX</sub>, which is the higher voltage of either V<sub>IN</sub> or V<sub>BAT</sub>. The POR voltage of the device is 1.8V.

#### 4.2 Power Path Management

The YHM2710 employs a pass-through power path structure with the LDO FET(Q1) between IN and SYS, and the battery FET (Q2) between SYS and BAT, to decouple the system from the battery. This allows for separate control between the system and the battery. The LDO output is always regulated to  $1.03 \times VREG$ . If the V<sub>IN</sub> is less than target LDO output, the LDO FET is fully turn on to pass through the current. The input current limit threshold is 550mA, when total current for charge and system load is above 550mA, the LDO FET will regulate the current. If the load further increases and V<sub>SYS</sub> falls below 2V, the device enters hiccup mode. The device also features RCB, when V<sub>SYS</sub> exceeds V<sub>IN</sub> by 5mV, the LDO FET will turn off.

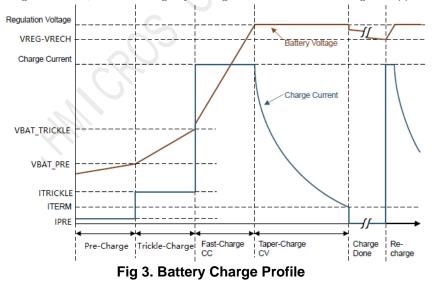

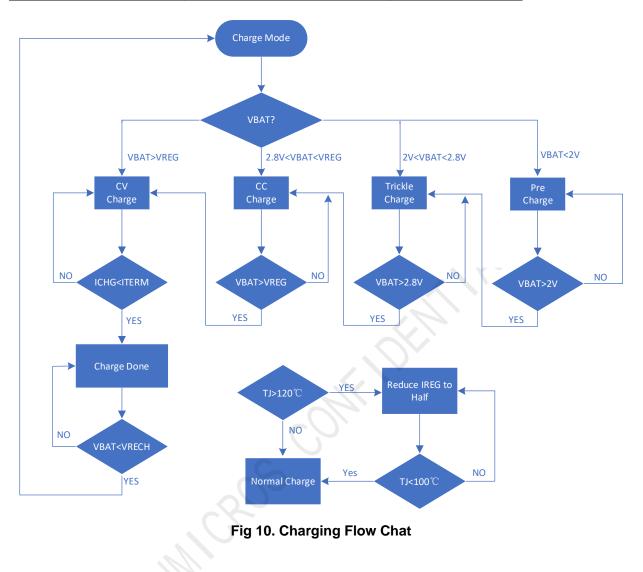

#### 4.3 Charge Profile

A charge cycle begins when  $V_{IN}$  rises above the UVLO threshold level. If the  $V_{BAT}$  is less than 2V, the charger enters Pre-charge mode. In this mode, the YHM2710 supplies 4mA charge current for dead battery. If the  $V_{BAT}$  is above 2V and less than 2.8V, the charger enters Trickle-charge mode. In this mode, the YHM2710 supplies approximately 1/20 the programmed charge current to bring the battery voltage up to a safe level for full current charging. When  $V_{BAT}$  rises above 2.8V, the charger enters constant-current mode, where the programmed charge current is supplied to the battery. When  $V_{BAT}$  approaches  $V_{REG}$ , the YHM2710 enters constant-voltage mode and the charge current begins to decrease. When the charge current drops to 1/20 of the programmed value, the charge cycle ends. When this voltage drops below the recharge threshold, another charge cycle begins and current is once again supplied to the battery.

#### 4.4 Charge Current Programming

The fast charge current is programmed using a single resistor from the ISNS pin to ground. The program resistor and the charge current are calculated using the following equations:

$R_{SNS} = 500/I_{REG}$ .

The charge current out of the BAT pin can be determined by ISNS pin voltage using the following equation:

YHMICROS

そい歌由子

$I_{BAT_CHG} = V_{ISNS} \times I_{RATIO_CHG}/R_{SNS}$

The discharge current into the BAT pin can be determined by ISNS pin voltage using the following equation:

$I_{BAT\_DCG} = V_{ISNS} \times I_{RATIO\_DIS} / R_{SNS}$

Connect ISNS pin to an ADC can monitor the charge and discharge current at any time for fuel gauging. When VBAT current is charging mode, IRATIO is 1000. In discharging mode, IRATIO is 5000. IRATIO can be read from ACMD. See below table for detail. In charge done or stop charge mode, the load is supplied by input power, the current monitor does not work.

| Mode<br>(02H [7:4]) | <b>VSYS&gt;VBAT</b><br>(05H [0]) | <b>ISNS_RATIO</b><br>(05H [4]) | VBAT Current<br>Direction | Q2_ratio |

|---------------------|----------------------------------|--------------------------------|---------------------------|----------|

| Chg Mode(12)        | 1                                | 0                              | Charging                  | 1000     |

| Chg Mode(12)        | 0                                | 0                              | Discharging               | 5000     |

| DisChg Mode(8)      | х                                | 0                              | Discharging               | 5000     |

#### Table 1. Current Ratio

#### 4.5 Low Dropout Fast Charge

YHM2710 supports low dropout fast charge, up to 1.5A charging current. When  $V_{IN}$  is above UVLO and below  $V_{REG}$ , Q1 will enter bypass mode. Then configure 00H[0]=1 to disable Q1 550mA current limit, 00H[3]=1 to disable headroom voltage and configure 01H[7:5] to choose the actual charging current for fast charge. Configure 03H[5]=1 can make Q2 fully on for directly charging.

#### 4.6 Battery Discharge

When  $V_{IN}$  is above UVLO threshold level, system is power by input from LDO FET. When  $V_{SYS}$  drop to below  $V_{BAT}$  by 5mV, the BAT FET turn on and battery start to supply current to system load. If  $V_{SYS}$  rise to  $V_{BAT}$  plus 5mV, BAT FET goes back to charge mode. The YHM2710 has an over-discharge current limit in discharge mode. Once the discharge current exceeds the programmable discharge current limit ( $10 \times I_{REG}$ ), the battery FET will regulate the current.

#### 4.7 Thermal Regulation and Thermal Shutdown

The YHM2710 will reduce the programmed charge current by half if the die temperature attempts to rise above 120°C. This feature protects the YHM2710 from excessive temperature and allows the user to push the limits of the power handling capability of a given circuit board without risk of damaging the chip. When the junction temperature reaches 150°C, both Q1 and Q2 turn off.

#### 4.8 System Short-Circuit Protection

The YHM2710 features SYS node short-circuit protection (SCP) for both the IN to SYS path and the BAT to SYS path. The system voltage is monitored continuously. When V<sub>SYS</sub> is lower than 2V consecutively for 60µs, the chip enters FAULT mode and both Q1 and Q2 will be turned off, hiccup 2ms later.

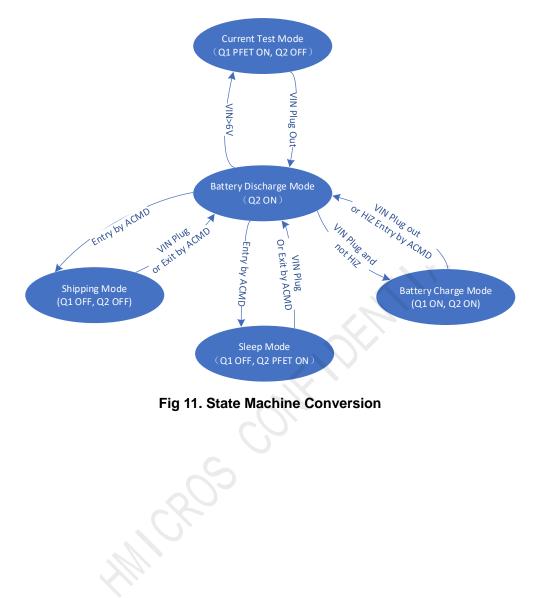

#### 4.9 Shipping Mode

At any point in the charge cycle, the YHM2710 can be put into shipping mode by Access command for 1.5s. In shipping mode, BAT FET turns off and the device only consume 150nA current from battery. Plug V<sub>IN</sub> to wake the YHM2710 up from shipping mode or pull STACMD to ground for 10.5s for the same.

#### 4.10 Current Test Mode

When  $V_{IN}$  exceed 6V for 2ms or set by Access command, the YHM2710 will enter current test mode. In this mode, Q2 turn off and the system current can be measured from input power supply. In test mode, the chip does not have over current protection, recommend add external OVP/OCP device in test cable. Remove  $V_{IN}$  to exit the current test mode.

#### YHMICROS **YHM2710** 爻以微电子 500mA Linear Charger with 150nA Shipping Mode Current

#### 4.11 Sleep Mode

YHM2710 can enter sleep mode by configuration. In sleep mode, battery Iq is only 150nA, the recommended discharge current is below 10mA. Before system wake up for large load, need to configure YHM2710 to exit sleep mode first.

#### 4.12 Hardware Reset

Pull STACMD down to GND for 10.5s, the device will shut down SYS for 200ms and automatically powering it back on. Choose a GPIO to connect to STACMD for communication which is high impedance when MCU is power off.

#### 4.13 Status

The STACMD pin can indicate charging, discharging and charge done status. When it is high, the battery is in discharging or charge done. When it is low, the battery is in charging.

### 5 Access Command

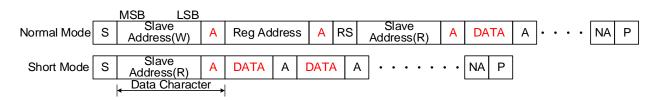

YHM2710 supports private Access Command(ACMD) from STACMD pin to configure the charger. Access command is a single wire communication protocol developed by YHMICROS. There are two type devices, master and slaver, in this protocol. The master can send control command to slaver and read slaver status. The slaver can only respond master instruction. Only the master can initial communication in Access command. The 7bit slave address of YHM2710 is 04H in normal mode.

#### 5.1 ACMD Physical Layer

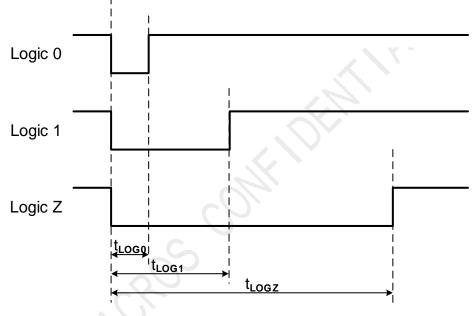

The communication line in ACMD is pull high with internal resistor. This line keeps in high voltage level if there is no communication signal. ACMD master or slaver can pull low this line if they need send data on this line. There are three waveforms to indicate three logic statuses (Logic 0, Logic 1 and Logic Z). These waveforms are different from their low pulse width. Please refer to below figure.

Figure 4. ACMD Logic Bit

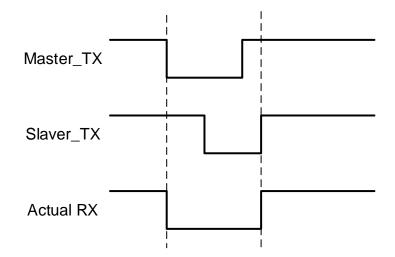

Logic 0's low voltage width is 8 tBIT, Logic 1's low voltage width is 26 tBIT and Logic Z's low voltage width is 60 tBIT. Logic 0 and Logic 1 are used to normal data communication. Logic Z is used as START, RE-START and STOP bit in data package. When device received Logic Z, it will reset internal status machine and intermediate variables in ACMD protocol. Please note, because master and slaver can pull down the communication line, the total low voltage period is AND operation for both master TX signal and slave TX. Figure 5 indicates this situation.

# YHM2710

# 500mA Linear Charger with 150nA Shipping Mode Current

### Figure 5. RX Behavior if Master and Slaver Drive Line Together

### Figure 6. ACMD Bit Timing

#### 5.2 ACMD Protocol Layer

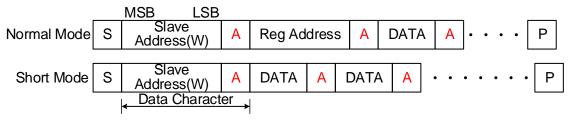

One ACMD data package is formed one START signal, data and STOP signal. Logic Z servers as START, RE-START and STOP signal role. When slaver receive one start signal, it reset status machine and wait for the data from line. It continues to receive data or send back to the master until it receives one STOP bit. Data character is formed with 8 bits data plus 1 bit parity. This parity is sent from the other side in communication. For example, if data is from the master, slave sends this parity as ACK for received one character data and the master check this bit to know the slave received data correct or not. Please note in the last data character, master send NACK to slave. NACK is NOT operation to ACK. Data character is MSB firstly. YHMICROS ACMD write and read operations include two options. One is normal device addressing mode. The other is short device addressing mode. In normal device address mode, the device has 6-bit device. In short device addressing mode, the device has 2-bit device address (4 devices) and 4-bit register address (16 registers). This means one ACMD line can support 4 slaver devices at most in short mode. But in this mode, the register number is less than the normal mode.

Figure 7. Write Operation in ACMD

### Figure 8 Read Operation in ACMD

In above figure, red bit is sent from slaver and the others is sent from master. The slave address character description is listed below.

| Mode   | Bit 7                                            | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2 | Bit 1  | Bit 0<br>Write/Read          | Α                   |

|--------|--------------------------------------------------|----------|----------|---------|----------|-------|--------|------------------------------|---------------------|

| Normal | mal Mode flag. Device Address<br>0: Normal mode. |          |          |         |          |       |        |                              | ACK from Slaver.    |

| Short  | 1: Short mode                                    | Device A | Address  | Registe | er Addre | SS    |        | flag.<br>0: Write<br>1: Read | Parity of Bit [7:0] |

|        |                                                  |          | Table 2. | Slave   | Addres   | s Cha | racter | - 7 / .                      |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

|        |                                                  |          |          |         |          |       |        |                              |                     |

#### **Register Map**

| Addr | ID      | Default | B7           | B6            | B5      | B4             | B3       | B2                    | B1                       | B0              |

|------|---------|---------|--------------|---------------|---------|----------------|----------|-----------------------|--------------------------|-----------------|

| 00H  | V_CTRL  | 00H     |              | VRE           | G[3:0]  |                | VHDRM    | VTRICKLE              | Q1_RCB                   | Q1_ILIM_DI<br>S |

| 01H  | I_CTRL  | 00H     |              | ICC[2:0]      |         | ITERM          | ITRICKLE | IPRE_VBAT             | SYS_TRA<br>CK            | RESERVED        |

| 02H  | MODE    | A0H     |              | MO            | DE[3:0] |                | M_SET    | BAT_OV_DIS            | RST_REG                  | HD_RST          |

| 03H  | CONFIG  | 00H     | RESERVE<br>D | ITERM_<br>DIS | CC_DIS  | WD_RST         | WD_EN    | VRECH                 | DIS_VIN_I<br>TEST        | FT_DEB_TI<br>ME |

| 05H  | STATUS1 |         | CH           | G_STATUS[     | 2:0]    | ISNS_RAT<br>IO | TSD_120  | TSD_150               | ISNS <ite<br>RM</ite<br> | VSYS>VBAT       |

| 06H  | STATUS2 |         |              | FSM MODE[3:0] |         |                | VBAT>2   | VBAT><br>VBAT_TRICKLE | VBAT_OV                  | VBAT_UV         |

| 07H  | STATUS2 |         | CV_BAR       |               |         | RESERVE<br>D   |          |                       |                          |                 |

| 08H  | ID      | A0H     | Vendor       |               |         |                |          | Revisio               | on                       |                 |

#### V\_CTRL Register

| Address: 00<br>Type: Read |             |          |                                                     |                                                        |  |

|---------------------------|-------------|----------|-----------------------------------------------------|--------------------------------------------------------|--|

| Bits                      | Name        | Defaults | Description                                         | Comment                                                |  |

|                           |             | 0        | 0000: 4.2V; 0001: 4.225V;                           |                                                        |  |

|                           |             | 0        | 0010: 4.25V; 0011: 4.275V;                          |                                                        |  |

|                           |             | 0        | 0100: 4.3V; 0101: 4.325V;                           | Battery regulation voltage.                            |  |

| 7:4                       | VREG[3:0]   | 0        | 0110: 4.35V; 0111: 4.375V;                          |                                                        |  |

| 7.4                       |             |          | 1000: 4.4V; 1001: 4.425V;                           | Default: 4.2V                                          |  |

|                           |             |          | 1010: 4.45V; 1011: 4.475V;                          |                                                        |  |

|                           |             |          | 1100: 4.5V; 1101: 4.525V                            |                                                        |  |

|                           |             |          | 1110: 4V; 11111: 4.1V;                              |                                                        |  |

| 3                         | VHDRM       | 0        | 0: 150mV Headroom voltage<br>1: No Headroom voltage | VIN VS VBAT                                            |  |

| 2                         | VTRICKLE    | 0        | 0: 2.8V<br>1: 3V                                    | Trickle-charge to fast charge threshold. Default 2.8V. |  |

|                           |             |          |                                                     | Input reverse blocking voltage                         |  |

| 1                         | Q1_RCB      | 0        | 0: $V_{SYS} - 5mV > V_{IN}$                         | threshold. Default trigger                             |  |

|                           |             |          | 1: Vsys +5mV > Vıℕ                                  | condition is $V_{SYS}$ - 5mV>V <sub>IN</sub> .         |  |

| 0                         | Q1_ILIM_DIS | 0        | 0: 550mA                                            | Disable Q1 current limit, default                      |  |

| -                         |             |          | 1: Disable Q1 ILIM                                  | is 550mA                                               |  |

\*Configure VHDRM=1 and Q1\_RCB=1 and CC\_DIS=1 to support bypass mode.

#### I\_CTRL Register

Address: 01h

Type: Read/Write

| Bits | Name       | Defaults | Description                                             | Comment                                              |

|------|------------|----------|---------------------------------------------------------|------------------------------------------------------|

|      |            |          | 000: 0.5×IREG; 001: 0.2×IREG;                           |                                                      |

|      |            | 0        | 010: 0.7×I <sub>REG</sub> ; 011: 0.9×I <sub>REG</sub> ; | Fast charge current Icc.                             |

| 7:5  | 5 ICC[2:0] | 0        | 100: I <sub>REG</sub> ; 101: 1.5×I <sub>REG</sub> ;     | Default: Icc = 0.5×IREG (000)<br>IREG is set by RSNS |

|      |            |          | 110: 2×I <sub>REG</sub> ; 111: 3×I <sub>REG</sub>       |                                                      |

| 4    | ITERM      | 0        | 0: 0.05×I <sub>REG</sub>                                | Termination current.                                 |

|   |           |   | 1: 0.1×I <sub>REG</sub>                                                                                                                                  | Default: 0.05×IREG<br>IREG is set by RSNS                                                                |

|---|-----------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 3 | ITRICKLE  | 0 | 0: 0.05×I <sub>REG</sub><br>1: 0.1×I <sub>REG</sub>                                                                                                      | Trickle charge current.<br>Default: 0.05×I <sub>REG</sub><br>I <sub>REG</sub> is set by R <sub>SNS</sub> |

| 2 | IPRE      | 0 | 0: 4mA<br>1: 12mA                                                                                                                                        | Pre charge current.                                                                                      |

| 1 | SYS_TRACK | 0 | 0: Disable SYS_TRACK,<br>VSYS=1.03*VREG during<br>charging, Q1 limit 550mA<br>1: Enable SYS_TRACK,<br>VSYS=1.053*VBAT during<br>charging, Q1 limit 275mA |                                                                                                          |

| 0 | RESERVED  |   |                                                                                                                                                          |                                                                                                          |

#### **MODE Register**

Address: 02h

Type: Read/Write

| Bits | Name       | Defaults | Description                                                                                                                                                                                                    | Comment                                                                                                                                              |

|------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4  | MODE[3:0]  | 1010     | 0000: RESET<br>0001: SHIPPING<br>0010: SLEEP<br>0011: ITEST<br>0100~0111: RESERVED<br>1000: DISCHARGE<br>1001: FAULT<br>1010: START<br>1011: SYS_PRE<br>1100: CHARGE<br>1101: CHARGE_DONE<br>1111: STOP_CHARGE | Valid when write M_SET=1<br>1111: STOP_CHARGE<br>0011: ITEST<br>0001: SHIPPING<br>0010: SLEEP<br>When exit above mode, must exit<br>to correct mode* |

| 3    | M_SET      | 0        | 0: No Action<br>1: Set FSM mode as MODE<br>[3:0]                                                                                                                                                               | Auto Clear                                                                                                                                           |

| 2    | BAT_OV_DIS | 0        | 0: Enable BAT OV<br>1: Disable BAT OV                                                                                                                                                                          |                                                                                                                                                      |

| 1    | RST_REG    | 0        | 0: No Action<br>1: Reset Reg                                                                                                                                                                                   | Auto Clear                                                                                                                                           |

| 0    | HD_RST 0   |          | 0: No Action<br>1: POR                                                                                                                                                                                         | Auto Clear                                                                                                                                           |

\*Check VIN OK before enter stop charge mode.

\*Write MODE[3:0]=1100 if want to exit Stop Charge Mode

\*Write MODE[3:0]=1000 if want to exit Sleep Mode

\*Write MODE[3:0]=1010 if want to exit ITEST Mode or Shipping Mode

#### **CONFIG Register**

Address: 03h

Type: Read/Write

| Bits | Name          | Defaults | Description                                                      | Comment                                                                                    |  |

|------|---------------|----------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| 7    | RESERVED      |          |                                                                  |                                                                                            |  |

| 6    | ITERM_DIS     | 0        | 0: Termination is enabled<br>1: Termination is disabled          |                                                                                            |  |

| 5    | CC-DIS        | 0        | 0: Q2 CC is enabled<br>1: Q2 CC is disabled                      |                                                                                            |  |

| 4    | WTD_RST       | 0        | 0: Default<br>1: Reset WD wait timer (Clear<br>to 0 after write) | Auto Clear                                                                                 |  |

| 3    | WD_EN         | 0        | 0: Disable<br>1: Enable watch dog                                | 16s WDI wait time. When timer<br>out, turn off Q1&Q2 for 200ms<br>then enter start up mode |  |

| 2    | VRECH         | 0        | 0: 200mV<br>1: 100mV                                             | Battery Recharge Voltage<br>Threshold                                                      |  |

| 1    | DIS_VIN_ITEST | 0        | 0: Enable<br>1: Disable                                          | 0: Enable V <sub>IN</sub> >6V enter current test mode.                                     |  |

| 0    | FT_DEB_TIME   | 0        | 0: 2ms<br>1: 100ms                                               | Fault hiccup time                                                                          |  |

|      |               |          |                                                                  |                                                                                            |  |

#### STATUS1 Register

Address: 05h

Type: Read Only

| Bits | Name                                                                    | Defaults  | Description                                        | Comment                       |                               |

|------|-------------------------------------------------------------------------|-----------|----------------------------------------------------|-------------------------------|-------------------------------|

|      |                                                                         |           | 000: Discharge                                     |                               |                               |

|      |                                                                         |           | 001: Pre-Charge                                    |                               |                               |

|      |                                                                         |           | 010: Trickle-Charge                                |                               |                               |

| 7:5  | CHG_STATUS                                                              | JS        | 011: CC Charge                                     |                               |                               |

| 7.5  | CIIG_SIAIOS                                                             |           | 100: Reserved                                      |                               |                               |

|      |                                                                         |           | 101: CV Charge                                     |                               |                               |

|      |                                                                         |           | 110: Reserved                                      |                               |                               |

|      |                                                                         |           | 111: Charge Done                                   |                               |                               |

| 4    |                                                                         |           |                                                    | 0: 5000                       | Discharge current sense ratio |

| 4    | ISNS_RATIO                                                              | SNS_RATIO | 1: Reserved                                        | Discharge current sense ratio |                               |

| 3    | TSD 120                                                                 |           | 0: TJ<120°C                                        |                               |                               |

| 3    | TSD_120                                                                 |           | 1: TJ>120°C                                        |                               |                               |

| 2    | 2 TOD 150                                                               |           | 0: TJ<150°C                                        |                               |                               |

| 2    | TSD_150                                                                 |           | 1: TJ>150°C                                        |                               |                               |

| 1    | ISNS <iterm< td=""><td></td><td>0: Isns&gt;Iterm</td><td></td></iterm<> |           | 0: Isns>Iterm                                      |                               |                               |

| I    |                                                                         |           | 1: I <sub>SNS</sub> <i<sub>TERM</i<sub>            |                               |                               |

| 0    |                                                                         |           | 0: V <sub>SYS</sub> <v<sub>BAT (Discharge)</v<sub> |                               |                               |

| 0    | 0 VSYS>VBAT                                                             |           | 1: V <sub>SYS</sub> >V <sub>BAT</sub> (Charge)     |                               |                               |

#### STATUS2 Register

YHMICROS

**爻**火|微电子

Address: 06h

Type: Read Only

| Bits | Name                  | Defaults | Description                                                                                                                                                                                                    | Comment |

|------|-----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:4  | FSM_MODE              |          | 0000: RESET<br>0001: SHIPPING<br>0010: SLEEP<br>0011: ITEST<br>0100~0111: RESERVED<br>1000: DISCHARGE<br>1001: FAULT<br>1010: START<br>1011: SYS_PRE<br>1100: CHARGE<br>1101: CHARGE_DONE<br>1111: STOP_CHARGE |         |

| 3    | VBAT>2                |          | 0: V <sub>BAT</sub> <2V<br>1: V <sub>BAT</sub> >2V                                                                                                                                                             |         |

| 2    | VBAT><br>VBAT_TRICKLE |          | 0: Vbat< Vbat_trickle<br>1: Vbat> Vbat_trickle                                                                                                                                                                 |         |

| 1    | VBAT_OV               |          | 0: VBAT< VREG+100mV<br>1: VBAT> VREG+100mV                                                                                                                                                                     |         |

| 0    | VBAT_UV               |          | 0: V <sub>BAT</sub> >2.4V<br>1: V <sub>BAT</sub> <2.4V                                                                                                                                                         |         |

#### STATUS3 Register

Address: 07h Type: Read Only

| Bits | Name     | Defaults | Description              | Comment                                                    |

|------|----------|----------|--------------------------|------------------------------------------------------------|

| 7    | CV_BAR   | 5        | 0: In CV<br>1: Not in CV | CV need meet below condition:<br>05H[7:5]=101 and 07H[7]=0 |

| 6:0  | RESERVED |          |                          |                                                            |

#### ID Register

Address: 08h

Type: Read Only

| Bits | Name    | Defaults | Description | Comment |

|------|---------|----------|-------------|---------|

| 7:4  | Vendor  | 1010     |             |         |

| 3:0  | Version | 0000     |             |         |

### 6 Control Flow Chat

Fig 9. Startup Flow Chat

MAX

0.573

0.170

0.403

1.040

0.690

0.240

# **YHM2710** 500mA Linear Charger with 150nA Shipping Mode Current

### **Package Dimensions**

### WLCSP-6 0.67x1.02

### **Ordering Information**

| Part Number | Temp Range    | Pin Package | Top Mark | MOQ  |

|-------------|---------------|-------------|----------|------|

| YHM2710W6T  | -40°C to 85°C | 6 WLCSP     | YW<br>L0 | 3000 |

T = Tape and reel.

YW: Date Code. Y = year, W = week.

L: The last number of LOTID.

0: YHM2710

HIMICROS CONFIDENTIAL

Email Requests to: <u>SALES@YHMICROS.COM</u> YHMicros Website: <u>WWW.YHMICROS.COM</u>